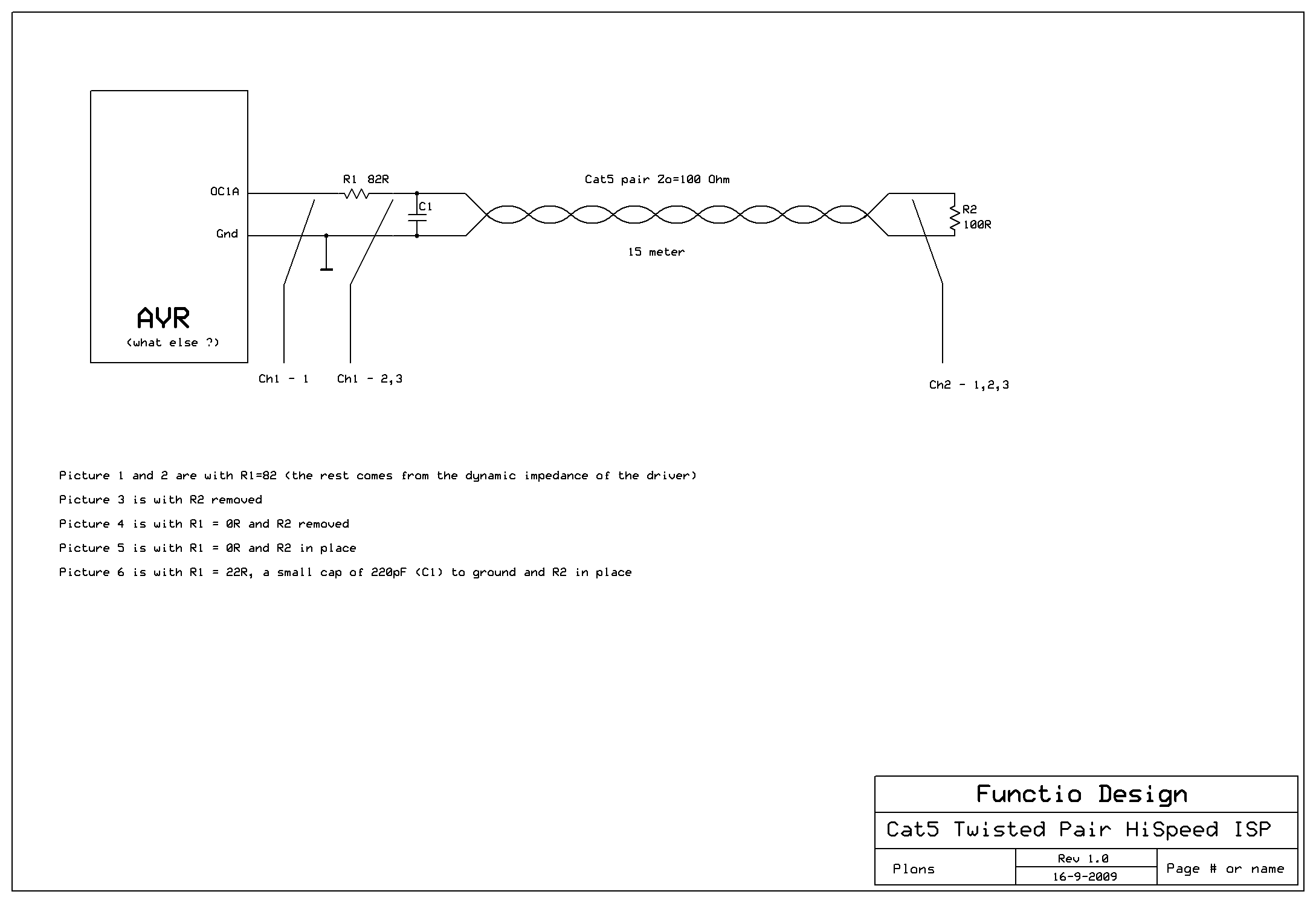

R1 and R2 are in place, C1=0pF

Ch2: measured over R2. The pulse amplitude is about 2V, so barely enough to meet the spec of TTL or HCT

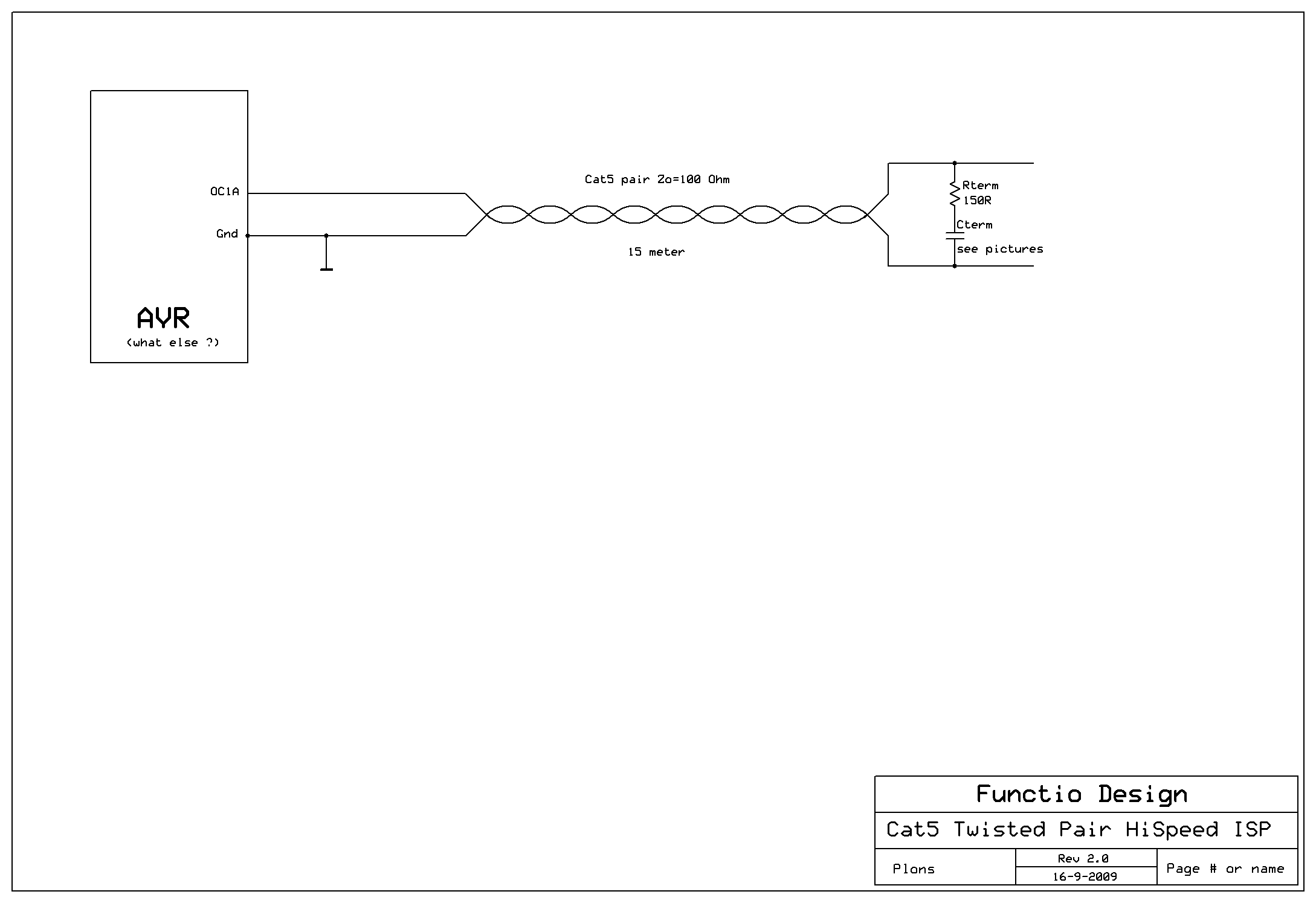

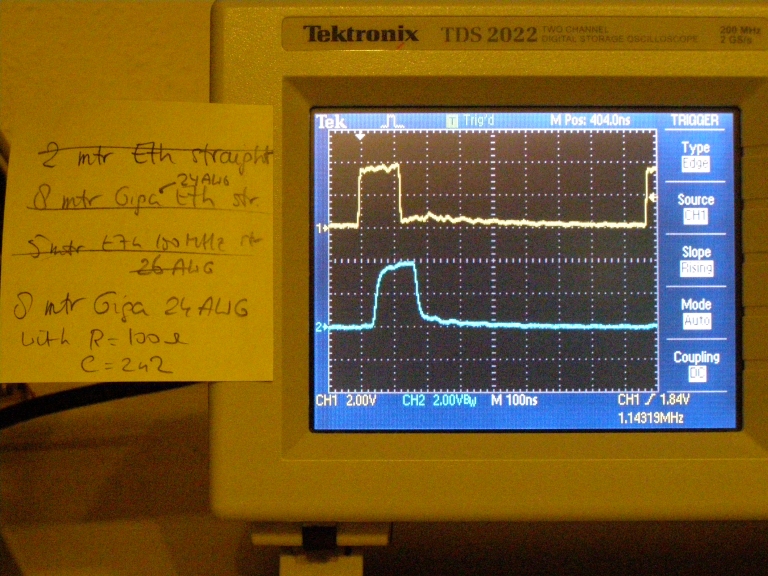

R2 is removed, so we lack termination. The pulse at the end of the cable travels back to the source, and that's the second pulse on Ch1

Nasty huh ?

Oh, BTW: using a narrow pulse is TEH way to go for these experiments.

The transmission line (the cable) is driven HARD .... and no termination by R2

How is that for a digital signal ?!